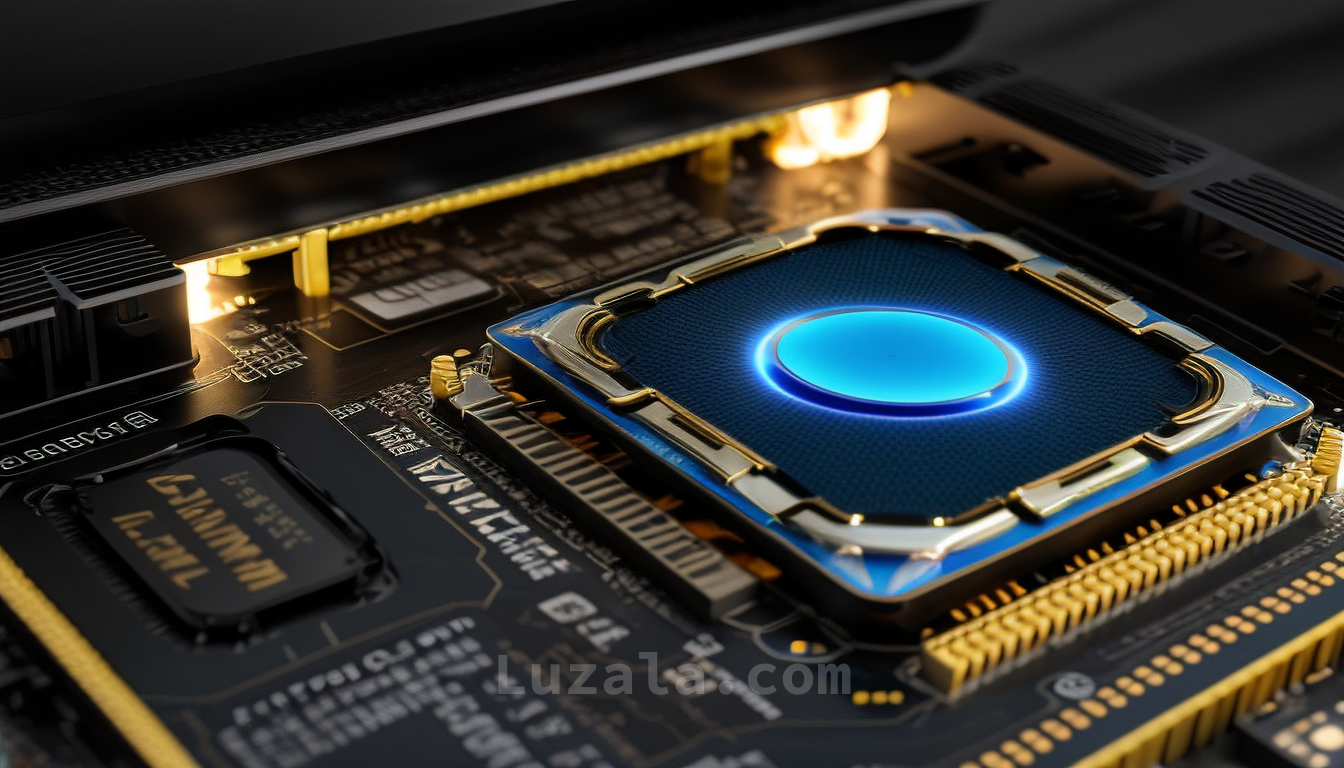

Intel's Meteor Lake: A Revolutionary Leap in CPU Architecture

Intels Meteor Lake is a revolutionary chiplet-based CPU architecture featuring Foveros 3D packaging and innovative power management, poised to transform the mobile market and drive PC innovation.

As the curtains lifted during the opening keynote at Intel's Innovation event in the vibrant city of San Jose, Chief Executive Officer Pat Gelsinger set the stage for a groundbreaking revelation – the forthcoming Meteor Lake client platform. For Intel, Meteor Lake signifies a pivotal moment as the company departs from the tumultuous Intel 7 node and embraces a new era characterized by the introduction of Foveros 3D packaging with EUV lithography for their forthcoming client mobile platform. This transformation heralds a significant shift in the architecture of Intel's consumer chips and brings with it a wave of innovations poised to reshape the mobile market.

Meteor Lake, Intel's inaugural chiplet-based consumer CPU, introduces a radical reconfiguration of the traditional CPU functions, dividing them into four distinct tiles: compute, graphics, SoC, and an I/O tile. Among these, the compute tile boasts a new pair of cores, the P-core named Redwood Cove, and the E-core known as Crestmont. These cores promise substantial IPC gains over their predecessors, but the most intriguing addition is the "Low Power Island" E-core, integrated directly into the SoC tile. This innovation allows lighter workloads to be shifted away from the power-hungry compute tile onto a more efficient and power-conscious tile. Another noteworthy inclusion is Intel's first Neural Processing Unit (NPU), nestled within the SoC tile, designed to deliver on-chip AI capabilities for various workloads and inferencing tasks.

With Meteor Lake, Intel aims to fortify its position in the fiercely competitive mobile market. It achieves this by overhauling the compute core hierarchy, enhancing integrated graphics capabilities through the Xe-LPG Arc-based graphics tile, and introducing an NPU that empowers AI-driven advantages. Meteor Lake not only ushers in these transformative improvements but also lays the foundation for Intel's modular disaggregation strategy, with Foveros 3D packaging poised to become a cornerstone of Intel's processor roadmap. The introduction of the Intel 4 process, as part of this evolution, acts as a stepping stone toward the forthcoming Intel 3 node, marking a clear path for the future of Intel's chip manufacturing technology.

Intel's Meteor Lake architecture represents a revolutionary leap, as articulated by Michelle Johnston Holhaus, the executive VP and GM of Intel's Client Computing Group (CCG) during Intel's Tech Tour 2023 in Penang, Malaysia. It signifies a significant performance advancement in comparison to Intel's existing client processors, aligning with their ambitious '5 nodes in 4 years' roadmap.

At its core, Meteor Lake leverages Intel's disaggregated architecture driven by Foveros packaging. This architecture optimizes both performance and energy efficiency, employing four distinct tiles interconnected through Intel's Foveros 3D packaging technology. These tiles encompass the compute tile, constructed on Intel 4, the graphics tile based on TSMC's N5 node, the SoC tile acting as the central hub via the embedded Network-on-Chip (NOC), a novel addition to Intel's client processors, and the I/O tile.

The NOC in Meteor Lake, in contrast to the intricate NOC structure in Agilex FPGAs, directly connects to the I/O fabric through the IoC, simplifying the architecture. This modular approach empowers a scalable power management architecture, enabling each tile to operate independently. Disaggregation also grants Intel the flexibility to choose specific silicon processes for each tile, breaking free from the limitations of a monolithic design. This approach not only enhances power efficiency and reduces packaging complexity but also facilitates cost savings for Intel by streamlining the manufacturing process through EUV lithography.

Unlike the mobile Raptor Lake, which employed Multi-Chip Packaging (MCP), Meteor Lake embraces Foveros BGA packaging. This decision introduces low-power die-to-die interconnects, with Intel confirming only a minimal power penalty of 0.15 to 0.3 picojoules (pJ) for communication between tiles. Foveros provides Intel with enhanced customizability, enabling tailored chip configurations based on specific requirements, be it emphasizing low power with more I/O or incorporating high-end features.

Moreover, Intel anticipates higher wafer yields on the Intel 4 node, as it occupies less wafer space for logic-based silicon. Meteor Lake's power management relies on a scalable system that accommodates the independent operation of each tile. Coordination between multiple Power Management Controllers (PMC) and system software ensures optimization for varying workloads. The architecture introduces a scalable fabric to tackle historical bottlenecks in areas like I/O, further enhancing energy efficiency and bandwidth.

Delving deeper into the power controllers within the Meteor Lake architecture, Intel integrates independent Power Management Controllers within each tile, aligning with the disaggregated approach. The NOC, I/O fabric, and individual tiles are equipped with PMCs, allowing flexible power management tailored to the specific demands of each package.

Meteor Lake stands as a monumental architectural shift, diverging from incremental updates seen in the past, as it marks the most significant transformation in client processors in four decades. It represents Intel's cornerstone strategy for driving PC innovation over the next decade. Examining the finer details of Meteor Lake, it leverages Intel's Foveros packaging technology, utilizing 3D chip stacking to overcome the limitations of traditional 2D chip layouts.

In Meteor Lake, the top and bottom layers feature bumps that facilitate interconnection between each die. Foveros FDI packaging offers a low-voltage CMOS interface, enabling power circuitry to operate at lower voltages and reducing the overall power envelope. Additionally, FDI supports both synchronous and asynchronous signaling, allowing efficient transmission of data blocks.

The construction of a Meteor Lake SoC entails a package substrate, serving as the foundation for the base tile. This base tile, with a 36µm die-to-die pitch, metal layering, and an operating power of 0.15 to 0.3 pJ at 2 GHz, acts as the underpinning for various logic components and chiplets.

The Meteor Lake architecture comprises four distinct tiles – Compute, SoC, GPU, and I/O – each offering unique capabilities and flexibility in terms of IP. Power management undergoes a significant overhaul, with each tile demanding its own independent power management. Intel introduces a hierarchical power management system that employs Power Management Controllers at multiple levels, including the NOC, I/O fabric, and individual tiles.

In conclusion, Meteor Lake embodies a transformative leap in the world of client processors, ushering in a new era of performance, efficiency, and scalability. Intel's innovative use of chiplets and Foveros packaging technology redefines the boundaries of what is possible in the realm of consumer CPUs, setting the stage for a future where modular disaggregation and cutting-edge silicon processes drive PC innovation to unprecedented heights. As the tech industry eagerly awaits the arrival of Meteor Lake, the promise of enhanced performance and efficiency ushers in a new era for Intel and the world of computing.

Download your fonts:

Mount Royal Font - Free Download

Swordfish Font - Free Download

Aniabellia Font - Free Download

Comments